RISC & CISC

-

Complex and Reduced instructions

- Standing up and walking would be a complex instruction

- Move arms, move knee, foot, leg, muscles etc.

- Standing up and walking would be a complex instruction

-

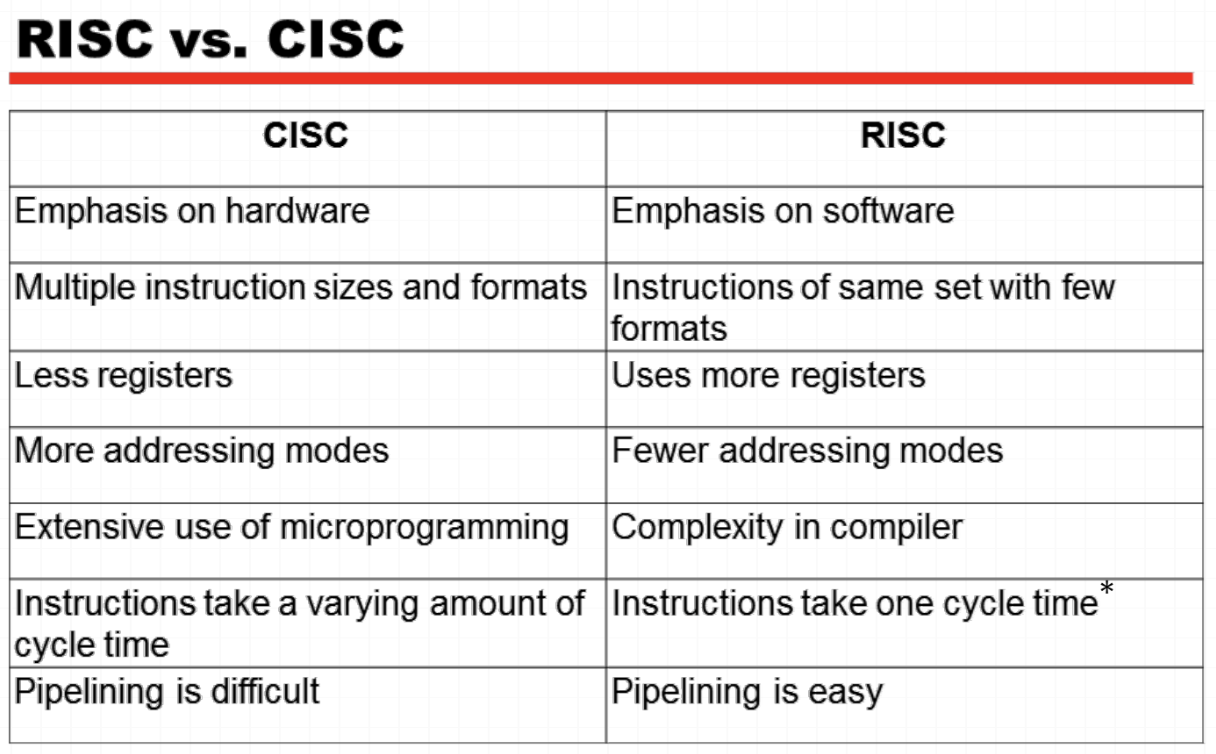

Modern PCs make use of a chip architecture known as CISC – in reality, modern CPUs are a mixture of CISC and RISC

- Instructions can be complex, involving multiple (maybe dozens) clock cycles – hence the term complex

- Loading and storing memory is incorporated into the instruction

-

RISC processors are architecturally designed to operate with a very reduced set of instructions

- Often (not always) a small set of primitive instructions

- Each instruction requires only 1 clock cycle, hence ‘reduced’ as in reduced complexity of instructions

- Memory actions are separate instructions

- Processing carried out using general purpose registers to assist with speed

- Can use pipelining to enable simultaneous instruction processing

- Often (not always) a small set of primitive instructions

-

RISC

- RISC uses simplified addressing modes

- Individual instructions deal with memory LOAD and STORE operations

- All other instructions use registers, simplifying the chip building process

- RISC are more likely to have a ‘Harvard memory model’

- Memory and instruction streams are conceptually separated

- g. different caches for instruction and data

- Memory and instruction streams are conceptually separated

-

-

Instruction examples:

- CISC

- Java: A = A * B;

- In a CISC processor there would be a specific instruction to achieve this, lets call it ‘MULT’:

- Load the two values into separated registers

- Multiply the operands in the execution unit

- Store the product in the appropriate register

- The entire task of multiplying two numbers can be completed with one instruction:

- MULT A,B (the assembly statement)

- MULT is known as a ‘complex instruction’. It operates directly on the computer’s memory banks and does not require the programmer to explicitly call any loading or storing functions

- In a CISC processor there would be a specific instruction to achieve this, lets call it ‘MULT’:

- Java: A = A * B;

- RISC

- Multiply two values together in a RISC processor:

- In a RISC processor there is no specific instruction to achieve this, instead we would have 4 separate instructions:

- LOAD R1, A ## load address A into register 1

- LOAD R2, B ## load address B into register 2

- PROD R1, R2, R3 ## multiply the two registers into R3

- STORE R3, A ## store register 3 back to address A

- The processing time is equal (in this case), but because there is no need for multiple instructions the processors design is simplified, allowing for more general purpose registers

- In a RISC processor there is no specific instruction to achieve this, instead we would have 4 separate instructions:

- Multiply two values together in a RISC processor:

- CISC

-

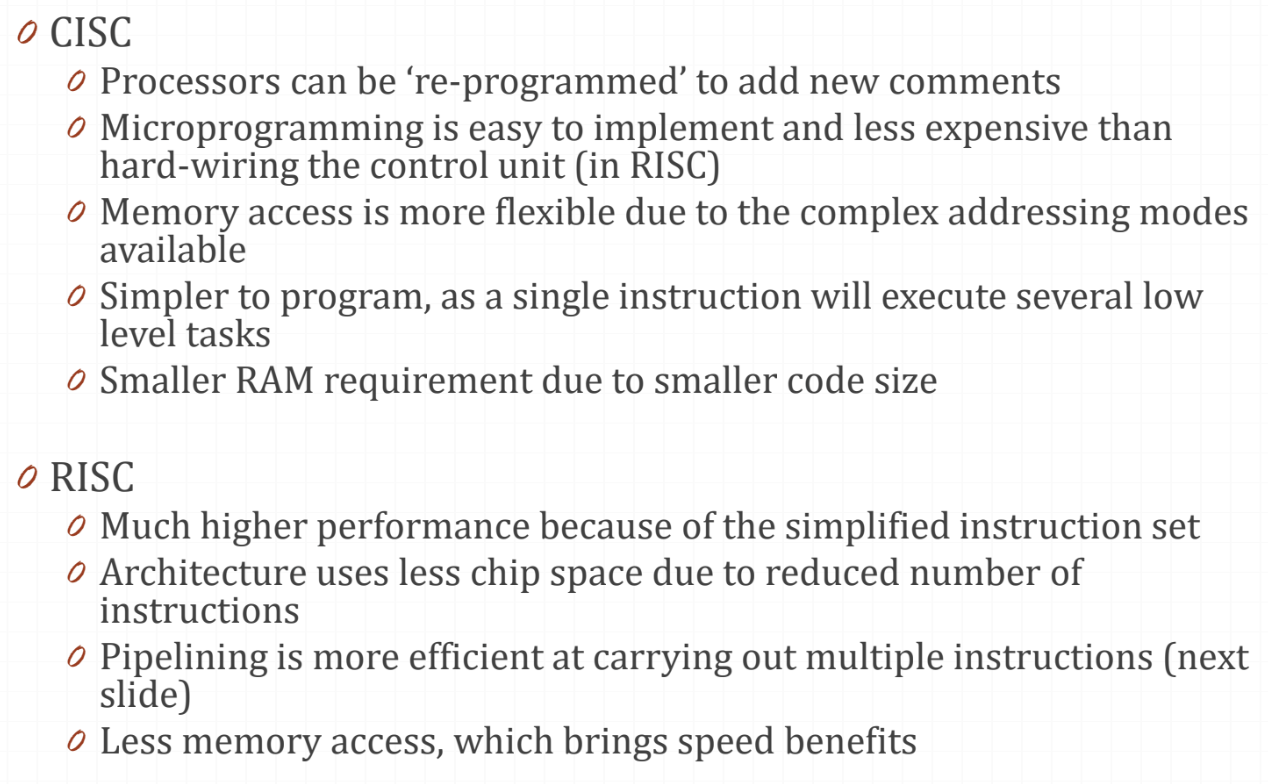

Summary:

- Modern processors have taken the best features from both architectures

- g. Modern RISC (e.g. MIPS architecture) include complex multiplication, division and multimedia instructions

- CISC chips are to some extent RIISC inside. Using microcode to define all the complex macro instructions (at the Control Unit level)

- g. Turn a complex command into multiple RISC commands within the chip